In the world of computer organization, the battle for processing supremacy often comes down to the fundamental language the processor speaks. This language is the Instruction Set Architecture (ISA). Whether you are a computer science student preparing for exams or a tech enthusiast curious about why Apple Silicon changed the industry, understanding the difference between RISC and CISC is the cornerstone of understanding modern computing.

While textbooks often present these two as binary opposites, the modern reality is a fascinating blend of engineering trade-offs, power efficiency, and raw performance. This guide goes beyond the basic definitions to explore the mechanics, the history, and the future of RISC vs CISC architecture.

The Core Difference Between Risc and Cisc: Quick Summary

If you are looking for a rapid answer for a test or quick reference, here is the fundamental distinction between the two architectures.

RISC (Reduced Instruction Set Computer) optimizes performance by using simple, single-cycle instructions, enabling efficient pipelining and low power consumption (e.g., ARM, Apple M1). CISC (Complex Instruction Set Computer) minimizes code size by using complex, multi-cycle instructions that perform composite operations directly in hardware (e.g., Intel x86, AMD). The primary difference lies in moving complexity from the hardware (CISC) to the software compiler (RISC).

What is CISC? (Complex Instruction Set Computer)

CISC full form is Complex Instruction Set Computer. To understand CISC, we must look at the computing landscape of the 1970s. Back then, memory (RAM) was incredibly expensive, and compilers were inefficient. The philosophy behind CISC was to move the complexity into the hardware to make the programmer’s life easier and the code shorter.

Key Characteristics of CISC

- Complex Instructions: A single instruction can execute low-level operations like loading from memory, an arithmetic operation, and storing back to memory.

- Variable Length Instructions: Instructions can take up different amounts of memory (e.g., 1 byte to 15 bytes).

- Microprogrammed Control Unit: The hardware contains a tiny internal program (microcode) to translate complex instructions into electrical signals.

- Memory-to-Memory Operations: CISC can manipulate data directly in memory without loading it into a register first.

Classic Example: The Intel x86 architecture (used in most Windows desktops and laptops) is the most successful implementation of CISC.

What is RISC? (Reduced Instruction Set Computer)

RISC full form is Reduced Instruction Set Computer. Emerging in the 1980s, engineers realized a phenomenon known as the 80/20 rule: programs spent 80% of their time executing only 20% of the available commands (mostly simple loads, stores, and adds).

RISC philosophy simplifies the hardware. By stripping away complex, rarely used instructions, chip designers could make the remaining simple instructions run incredibly fast—ideally in a single clock cycle.

Key Characteristics of RISC

- Simple Instructions: Each instruction performs a very specific, small task.

- Fixed Length Instructions: Every instruction is the same size (e.g., 32 bits), making decoding predictable and fast.

- Hardwired Control Unit: The logic is etched directly into the silicon, which is faster than microcode.

- Register-Heavy: Operations happen mainly in registers. You must explicitly move data from memory to a register (LOAD) before working on it.

Classic Example: ARM architecture (used in smartphones, tablets, and the Apple M-series chips).

Visualizing the Difference: The Code Comparison

To truly grasp the difference, look at how each architecture handles a simple multiplication command (A = A * B).

CISC Approach (x86 style):

CISC handles this in one powerful line. The hardware handles the loading and storing automatically.

MULT 2:3, 5:2 ; Multiply value at memory 2:3 by 5:2 and store backRISC Approach (ARM style):

RISC requires you to be explicit. You must load data into registers, perform the math, and save it back. It is a “Load/Store” architecture.

LOAD A, 2:3 ; Load data from memory into Register A

LOAD B, 5:2 ; Load data from memory into Register B

PROD A, B ; Calculate product of A and B

STORE 2:3, A ; Move result from Register A back to memoryWhile the RISC code is longer (4 lines vs 1), each line executes extremely fast (often 1 cycle), whereas the single CISC line might take many cycles to complete.

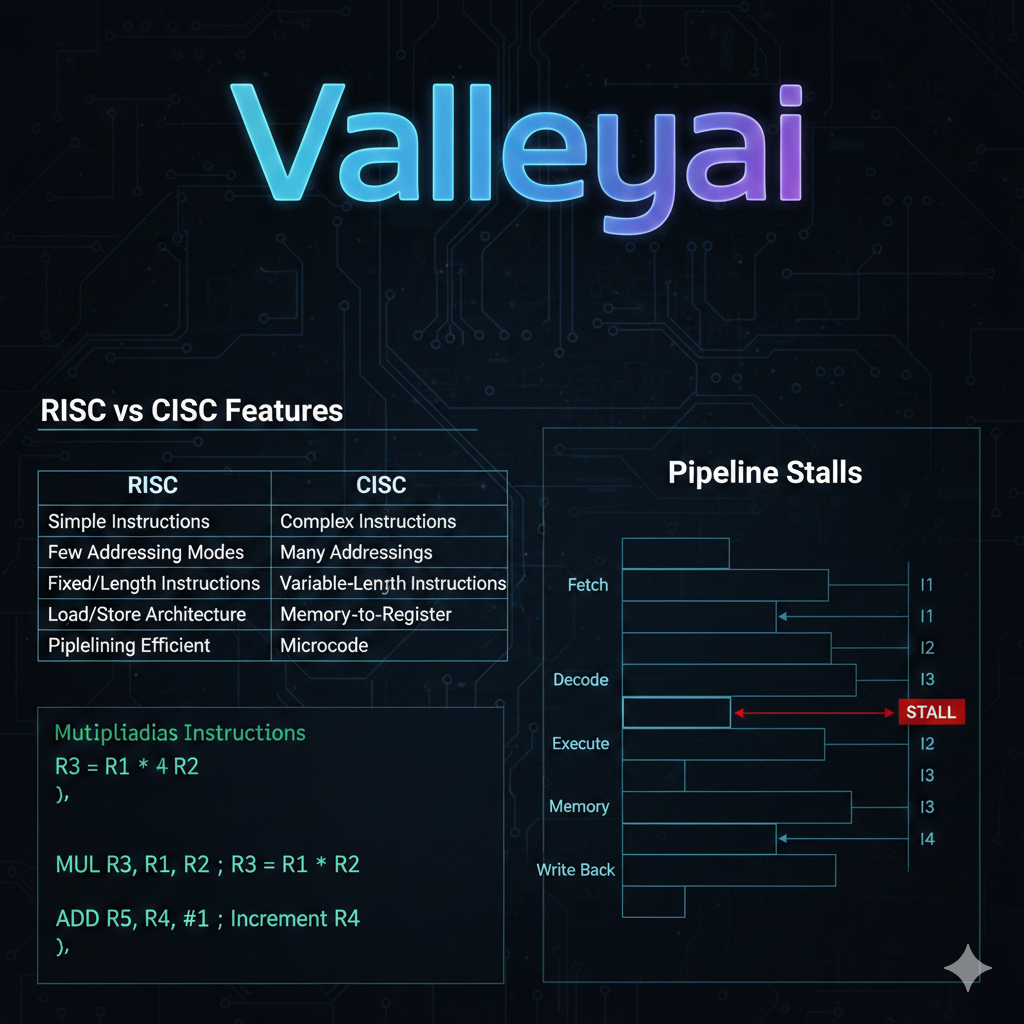

Comparison Table: RISC vs CISC

This table highlights the technical differences crucial for academic exams and architectural analysis.

| Feature | RISC (Reduced Instruction Set Computer) | CISC (Complex Instruction Set Computer) |

|---|---|---|

| Instruction Complexity | Simple, primitive instructions (1 cycle). | Complex instructions (multiple cycles). |

| Instruction Length | Fixed length (easy to decode). | Variable length (complex to decode). |

| CPI (Cycles Per Instruction) | Approximates 1 (Single cycle). | High (varies from 2 to 100+). |

| Pipelining | Highly efficient due to uniform timing. | Difficult due to variable instruction duration. |

| Control Unit | Hardwired (Faster). | Microprogrammed (Flexible). |

| Register Set | Large number of general-purpose registers. | Small number of registers. |

| Addressing Modes | Simple, Limited | Complex, Diverse |

| Code Size | Larger (requires more lines of code). | Smaller (complex instructions do more). |

| Hardware vs. Software | Complexity lies in the Compiler (Software). | Complexity lies in the Processor (Hardware). |

| Examples | ARM, MIPS, RISC-V, SPARC. | Intel x86, AMD, VAX, Motorola 68000. |

Deep Dive: The Mechanics of Performance

To truly understand which is better, RISC or CISC?, we need to look at the engineering concepts that drive speed.

1. Pipelining and Execution Speed

Pipelining is the process of fetching the next instruction while the current one is being executed. Think of it like a factory assembly line.

- RISC Advantage: Because every RISC instruction is the same size and takes roughly the same time (1 cycle), the pipeline flows smoothly. There are rarely jams in the line.

- CISC Challenge: If one instruction takes 1 cycle and the next takes 50 cycles, the pipeline stalls. This unpredictability makes high-speed pipelining difficult in pure CISC machines.

2. The Semantic Gap

Computer architecture creates a bridge between high-level languages (like C++ or Python) and machine code. This is called the Semantic Gap.

- CISC was designed to close this gap by creating machine instructions that looked like high-level code.

- RISC accepts a wider gap, relying on smart compilers to translate high-level code into long sequences of simple machine code.

3. Power Consumption

This is the deciding factor in the mobile era. CISC processors require complex decoding logic (transistors) to understand their varied instructions. More transistors meant more heat and power usage. RISC chips, with their simpler logic, are inherently more energy-efficient, which is why ARM dominates the battery-powered world (smartphones).

The Iron Law of Performance

Computer architects use a specific equation to decide between these architectures. It represents the trade-off at the heart of the RISC vs CISC debate:

Time/Program = (Instructions/Program) × (Cycles/Instruction) × (Seconds/Cycle)

- CISC tries to minimize the Instructions per Program by making instructions powerful.

- RISC tries to minimize the Cycles per Instruction (CPI) by making instructions simple.

Modern winners are those that balance this equation most effectively.

The Modern Convergence: x86 vs ARM

Most textbooks stop at the definitions above, but that information is partially outdated. In the modern era, the line between RISC vs CISC architecture has blurred significantly.

Is Intel i7 RISC or CISC?

Strictly speaking, Intel Core i7 and i9 processors are CISC (x86). However, Intel pulled a brilliant engineering trick. Inside the processor, a hardware decoder breaks down complex CISC instructions into smaller, RISC-like operations called Micro-ops (uOps).

- The Interface: The software sees CISC (backward compatibility).

- The Core: The execution unit runs these fast, simple micro-ops similarly to a RISC machine.

Does Apple use RISC or CISC?

Apple Silicon (M1, M2, M3) is based on ARM, which is a RISC architecture. However, Apple has added specialized hardware instructions (accelerators) for complex tasks like video encoding and encryption. This adds a layer of “complexity” typically associated with CISC, proving that modern high-performance chips borrow the best from both philosophies.

RISC vs CISC Advantages and Disadvantages

Advantages of RISC

- Speed: Simple instructions allow for higher clock speeds and efficient pipelining.

- Design Simplicity: Designing the chip takes less time and fewer transistors, reducing cost.

- Energy Efficiency: Lower power consumption makes it ideal for mobile devices and laptops.

Disadvantages of RISC

- Code Size: Programs require more memory because multiple instructions are needed to perform a task that CISC does in one.

- Memory Bandwidth: Because code is longer, the processor must constantly fetch more instructions from RAM, potentially causing a bottleneck.

- Compiler Dependence: The performance relies heavily on the compiler’s ability to optimize code.

Advantages of CISC

- Code Compactness: Programs are smaller, saving storage and RAM (critical in the early days).

- Less RAM Access: Complex instructions can operate directly on memory, reducing the need to shuffle data back and forth to registers.

- Backward Compatibility: Modern x86 chips can still run software written decades ago.

Disadvantages of CISC

- Hardware Complexity: The decoding logic is heavy, generating more heat and consuming more power.

- Inefficiency: The “20%” of rarely used complex instructions take up silicon space but offer little performance gain for most tasks.

The Rising Challenger: RISC-V

No modern discussion is complete without mentioning RISC-V. Unlike ARM (which is proprietary and requires a license), RISC-V is an open-source standard based on RISC principles. It is rapidly gaining traction in IoT and specialized AI chips, allowing companies to design custom processors without paying licensing fees to ARM or Intel. It represents the purest form of the RISC philosophy in the modern era.

Conclusion

The debate of RISC vs CISC has evolved from a war of philosophies into a convergence of technologies. While CISC (Intel/AMD) continues to dominate the desktop and server market through brute force and micro-op translation, RISC (ARM) has conquered the mobile world and is now challenging desktops via Apple Silicon.

For students and engineers, the takeaway is clear: RISC prioritizes hardware simplicity and pipeline efficiency, while CISC prioritizes code density and hardware complexity. Understanding these trade-offs is key to mastering computer architecture.

Frequently Asked Questions (FAQs)

Why is RISC faster than CISC?

RISC is often considered faster for throughput because it aims for a Cycles Per Instruction (CPI) of 1. By executing simple instructions in a single clock cycle, it maximizes the efficiency of the instruction pipeline. However, raw speed also depends on clock frequency and parallel processing.

Which is better, RISC or CISC?

Neither is universally better; it depends on the use case.

Choose RISC (ARM) for battery-dependent devices like phones, tablets, and IoT devices where power efficiency is paramount. Choose CISC (x86) for high-performance desktops, gaming rigs, and legacy servers where raw power and software compatibility are the priority.

What is the main role of the compiler in RISC?

In RISC, the hardware is simple, so the complexity is shifted to the software. The compiler plays a critical role in arranging instructions to prevent pipeline stalls and converting high-level code into efficient sequences of simple commands.

Why does RISC require more RAM than CISC?

RISC requires more RAM because its code density is lower; a single complex task that takes one line of code in CISC might require multiple simple lines in RISC, resulting in a larger executable file size.

What is the Iron Law of processor performance?

The Iron Law states that CPU Time = (Instruction Count) × (CPI) × (Clock Cycle Time). RISC reduces CPI, while CISC attempts to reduce Instruction Count.

Kaleem

My name is Kaleem and i am a computer science graduate with 5+ years of experience in Computer science, AI, tech, and web innovation. I founded ValleyAI.net to simplify AI, internet, and computer topics also focus on building useful utility tools. My clear, hands-on content is trusted by 5K+ monthly readers worldwide.